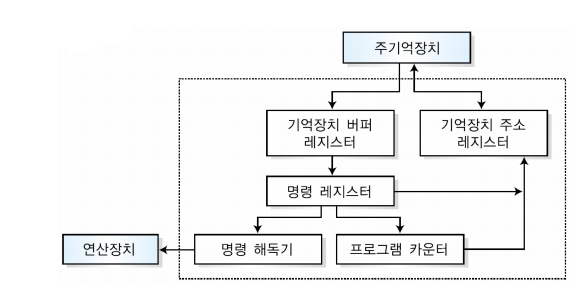

1. 제어장치

-> 주기억장치에서 저장된 명령을 해독하고, 해독한 명령어 지시하는 연산이 수행되도록 해당 장치에 제어신호 전달

-> 레지스터, 명령어 해독기, 프로그램 카운터를 비롯한 각종 장치 필요

● 프로그램 카운터 : 다음에 인출될 명령어 주소 저장 (레지스터의 일종으로 취급)

● 명령 레지스터 : 현재 실행중인 명령어 저장 = 가장 최근에 인출될 명령어

-> 주기억장치에서 명령을 인출하여 기억장치 버퍼 레지스터와 명령 레지스터에 임시저장하고 명령 해독기에서 명령어를 해독

-> 마지막으로 해독된 내용들은 연산장치로 전달

2. 명령어 사이클(=데이터 경로 사이클)

-> 명령어 인출, 해독, 실행 사이클로 진행

-> 인터럽트 사이클 : 명령어 사이클이 끝나고 인터럽트 유무 점검, 만약 인터럽트 있으면 인터럽트 처리 루틴을 실행

1) 인터럽트란 끼어들기를 의미

2) 인터럽트 발생시킨 장치의 작업을 우선 실행

3) 다른 작업 중이었는데 인터럽트 발생하면 하고 있던 프로그램의 중요 데이터는 주기억장치에 저장하고 인터럽트 장치 작업을 먼저 수행

4) 인터럽트 서비스 루틴 : 인터럽트 처리하기 위해 실행되는 새로운 프로그램 루틴

t0 : 복귀주소를 저장하기 위해서 프로그램 카운터 내용을 MBR로 이동

t1 : SP(스택 포인터)를 MAR로 이동시키고 인터럽트 처리 루틴 시작 주소를 PC에 적재,

SP는 MBR에 저장되어 있는 내용을 스택에 저장하기 위해서 저장할 위치를 지정하는 데 사용

t2 : MBR의 내용을 MAR에 근거하여 해당 스택 포인터의 스택에 저장

-> 각 명령어 사이클은 여러 개의 작은 단위로 구성

-> 제어 장치를 설계하려면 더 작은 단위의 마이크로 연산으로 분할

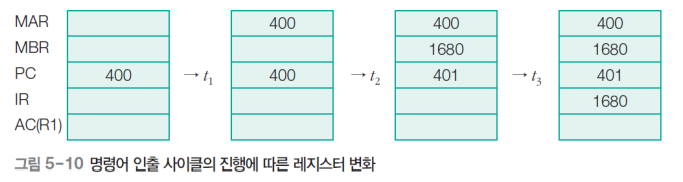

2-1. 명령어 인출 사이클

-> 모든 명령어 실행의 첫 번째 단계

-> 다음에 실행할 명령어를 주기억 장치에서 읽어 오는 과정

t1 : PC -> MAR -> 주소버스

t2 : M[MAR] -> 데이터 버스 -> MBR

t3 : MVR -> 명령 레지스터(IR)

-> 명령어 인출 사이클이 진행되는 동안 프로세서의 레지스터 변화 과정

t1 : MAR <- (PC)

t2 : MBR <- M[MAR], PC <- (PC) + I

// I는 명령어의 크기

t3 : IR <- (MBR)

-> 마이크로 연산을 그룹으로 묶을 때 두 가지 규칙 지켜야 함

1) 연산의 순서 준수 : MAR<-(PC) 는 반드시 MAR의 주소를 사용하기 떄문에 MBR <- 주기억장치 앞에 와야 함

2) 충돌 피해야 함 : 동시에 동일한 레지스터에서 읽고 쓰려고 해서는 안 된다.

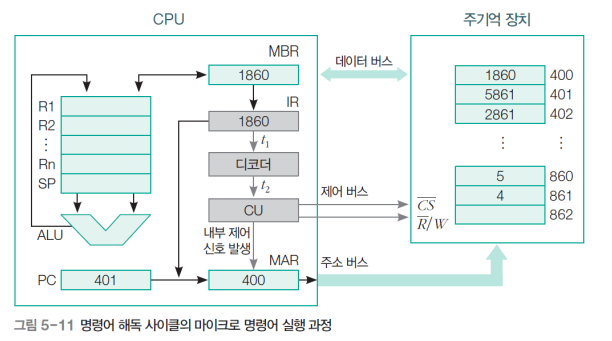

2-2. 명령어 해독 사이클

-> 명령 레지스터의 내용 중에서 오퍼랜드는 제외한 오피코드만 해독기로 전달

-> 해독기는 제어 기억 장치에서 명령 연산에 해당되는 마이크로 루틴을 찾아 해독

-> 해독된 명령어에 대한 후속 마이크로 연산 발생

2-3. 명령어 실행 사이클

-> 해독된 명령어를 실행하는 사이클

-> 해독된 명령어에 대한 후속 마이크로 연산 발생

IR : operand ➔ MAR ➔ 주소 버스

M[MAR] ➔ MBR ➔ 데이터 버스

MBR ➔ R1

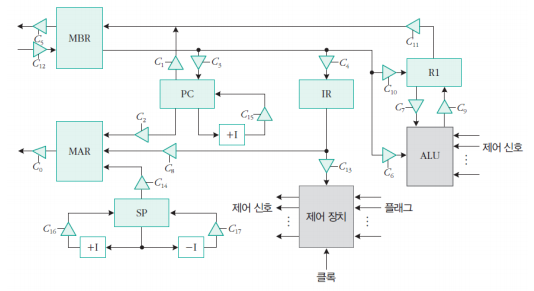

3. 프로세서 제어

-> 제어 장치의 특성

1) 프로세서의 기본 장치 정의

2) 프로세서가 수행하는 마이크로 연산 나열

3) 마이크로 연산을 할 수 있도록 제어 장치가 수행해야 할 기능 결정

-> 모든 마이크로 연산은 다음 범주 중 하나

1) 한 레지스터에서 다른 레지스터로 데이터 전송

2) 레지스터에서 외부 인터페이스로 데이터 전송

3) 외부 인터페이스에서 레지스터로 데이터 전송

4) 입출력 레지스터를 사용하여 산술 또는 논리 연산 수행

-> 제어 장치는 다음 제어 신호를 동시에 전송하여 명령 흐름 제어

1) 제어 신호는 MAR 내용을 주소 버스에 전달

2) 제어 버스에 메모리 읽기 제어 신호 전송

3) 데이터 버스 내용을 MBR에 저장할 수 있도록 제어 신호 전송

4) PC 내용에 I를 더해 PC에 다시 저장하는 제어 신호

4. 파이프라이닝

: 명령 하나를 단계 여러 개로 나누어 각각을 독립적인 장치에서 동시에 실행하는 기술

-> 5단계 파이프라인

S1 : 메모리에서 명령어를 인출

S2 : 명령어를 해독하고 명령어 형태를 결정하며 필요한 피연산자 결정

S3 : 레지스터 또는 메모리에서 피연산자 결정

S4 : 명령어 연산 수행

S5 : 결과를 레지스터에 저장

-> 파이프 라이닝을 사용하면 지연 시간과 프로세서 대역폭 간 균형을 유지할 수 있음

● 데이터 해저드 : 파이프 라인에서 앞서가는 명령의 ALU 연산 결과를 레지스터에 기록하기 전에 다른 명령에 이 데이터가 필요한 상황을 의미 = 데이터 의존성

1) 문제 발생 : 앞의 명령 결과가 다음 명령 입력으로 사욜될 때 파이프 라인 시스템에서

2) 해결 방안 : 레지스터에 저장되기 전 ALU 결과를 직접 다음 명령에 전달 = 데이터 포워딩

버블을 명령 사이에 끼워 넣어 프로그램 실행을 1 또는 2단계 지연시킴

● 제어 해저드 : 파이프 라인 CPU 구조의 분기 명령이 실행될 때 발생, 이미 파이프 라인에 적재되어 실행되고 있는 이어지는 다른 명령들이 더 이상 필요가 없어지므로 발생함

1) 해결 방안 : 지연 슬롯(NOP나 분기 명령과 무관한 명령을 끼워 넣는 것)을 넣고 분기 목적지 주소를 계산하는

과정을 파이프 라인 속에 넣음

분기 예측 알고리즘 이용

● 구조적 해저드 : 서로 다른 단계에서 동시에 실행되는 명령이 컴퓨터 내의 장치 하나를 동시에 사용하려고 할 때 발생

1) 해결 방안 : 하버드 구조 사용

분리 캐시를 사용하여 충동을 피하게 만들어 주기

'공부 > 컴퓨터구조' 카테고리의 다른 글

| [11주차]기억장치(2) (0) | 2021.05.13 |

|---|---|

| [10주차]제어장치(2), 기억장치 (0) | 2021.05.06 |

| [6주차]레지스터, 컴퓨터 명령어, 주소 지정 방식, 컴퓨터 시스템의 동작 (0) | 2021.04.09 |

| [4주차]디지털 논리 회로-조합 논리 회로,집적 회로 /중앙 처리 장치~ (0) | 2021.04.03 |

| [3주차]디지털 논리회로-불 대수 (0) | 2021.03.26 |